Journals

Kulkarni, A.; Ouameur, M.A.; Massicotte, D. “Energy Efficient Wireless Signal Detection: A Revisit through the Lens of Approximate Computing.” Electronics 2024, 13, 1274. View Paper: Electronics

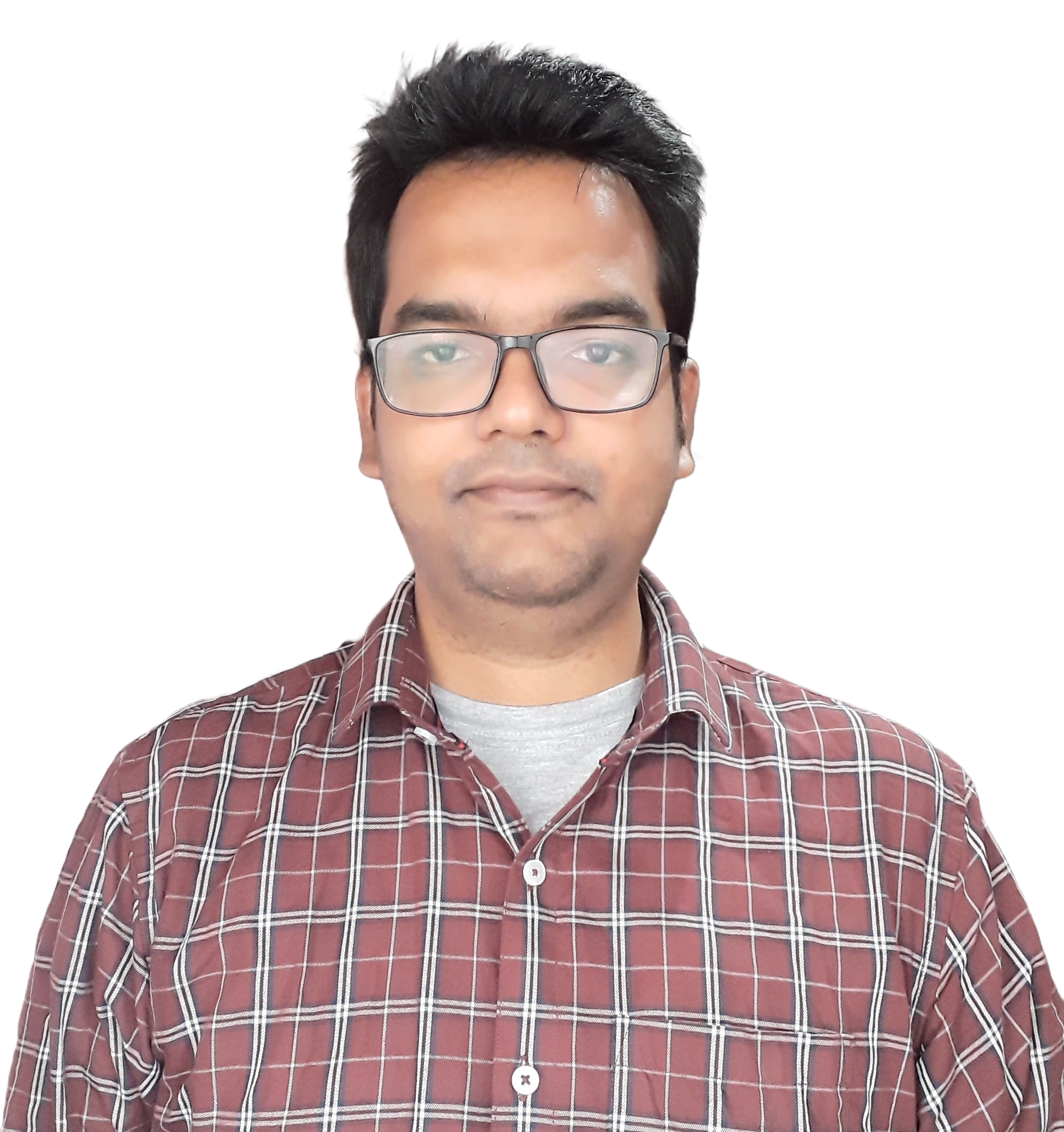

Description: In the quest for energy efficiency in next-generation communication systems, approximate computing is emerging as a useful technique. The use of approximate multiplication in wireless signal detection is systematically explored in this work, using Truncated Multiplication (TM) in Quadrature Phase Shift Keying (QPSK) Minimum Mean Square Error (MMSE) detection as an example. This work also aims to address the challenge of linking the level of approximation and the Quality-of-Service (QoS) in the system. Approximate Multiplication Noise (AMN) model captures the irregularities caused by approximation in wireless signal detection, helping analyze signal fidelity and system resilience. The approximation analysis highlights energy efficiency gains, while signal fidelity analysis enables the prediction of system output for varying approximation levels, improving system stability. Higher approximation levels are advantageous in low Signal-to-Noise Ratio (SNR) environments, whereas lower approximation levels are beneficial in high SNR scenarios.

A. Kulkarni, M. A. Ouameur and D. Massicotte, “Logic cloning based approximate signed multiplication circuits for FPGA” in Microelectronics Journal, Volume 145, 2024, View Paper: Microelectronics

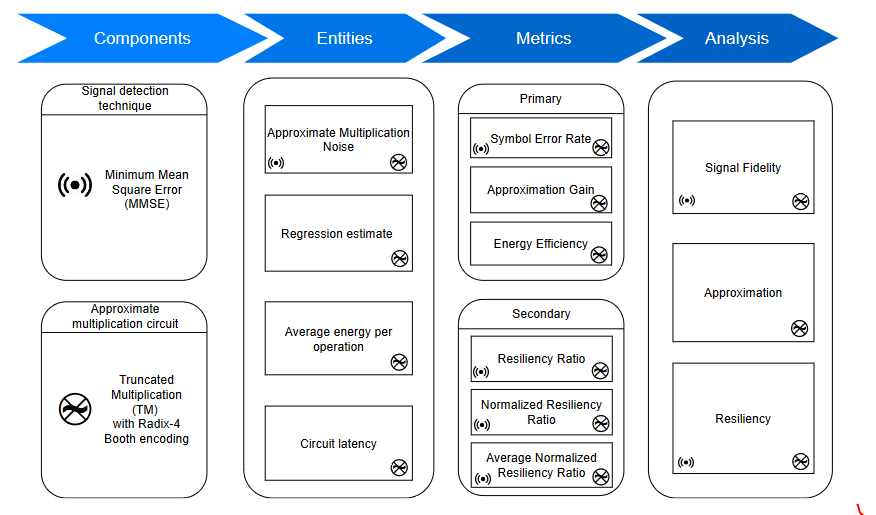

Description: As the complexity of hardware circuits increases, approximate circuit techniques are becoming more important to balance system accuracy, hardware resource efficiency, and energy conservation. For FPGA-based computation-intensive arithmetic multiplication, Logic Cloning (LC) is a method that introduces controlled approximation systematically. LC-Baugh Wooley (BW) circuits excel in error performance with precise approximation, while LC-Booth circuits are known for their reduced Look-Up Table (LUT) resource consumption. These LC approximate multiplication circuits effectively decrease LUT resource consumption and lower the Power Delay Product (PDP) when compared to their accurate counterparts. In terms of symbol error-rate performance for Zero Forcing (ZF) Multiple Input Multiple Output (MIMO) uplink detection, these LC approximate multiplication circuits demonstrate robust performance. Particularly, LC-BW circuits closely match the accuracy of ZF detection, with LC-Booth circuits following closely behind.

A. Kulkarni, M. A. Ouameur and D. Massicotte, “Hardware Topologies for Decentralized Large-Scale MIMO Detection Using Newton Method,” in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 68, no. 9, pp. 3732-3745, Sept. 2021, doi: 10.1109/TCSI.2021.3097042. View Paper: UQTR IEEE

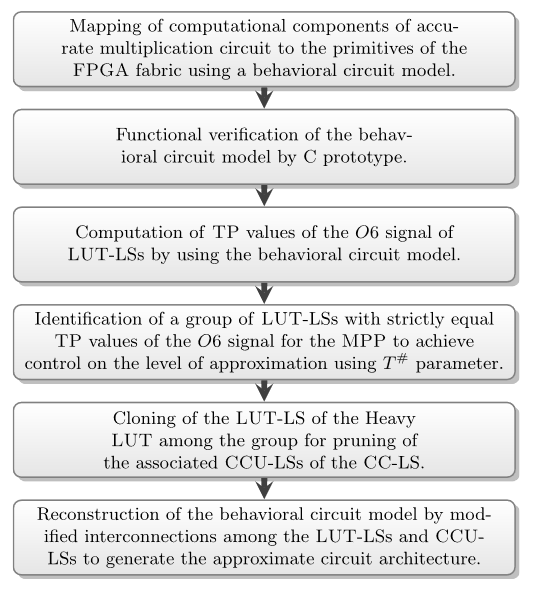

Description: Centralized Massive Multiple Input Multiple Output (MIMO) uplink detection techniques for baseband processing possess severe bottleneck in terms of interconnect bandwidth and computational complexity. This problem has been addressed in the current work by adapting the centralized Newton method for decentralized MIMO uplink detection leveraging several Base Station antenna clusters. The proposed decentralized Newton (DN) method achieves error-rate performance close to centralized Zero Forcing detector as compared to other decentralized techniques. Two hardware topologies, namely the ring and the star topologies, are proposed to assess and discuss the trade-off among interconnect bandwidth and throughput, in comparison with contemporary decentralized MIMO uplink detection techniques. As such the following findings are elaborated. On BS antenna cluster scaling for different MIMO system configurations, the ring topology provides high throughput at constant interconnect bandwidth, while the star topology provides lower latency with a deterministic variation in the hardware resource consumption. Due to strategic optimizations on the hardware implementation, additional user equipment can be allotted at a fractional increase in Field Programmable Gate Array resource consumption, improved energy efficiency, and increased transaction of bits per Joule. The ring topology can process additional subcarrier at a fractional increase in latency and improved system throughput.

Conferences

A. Dubey, A. Kulkarni, A. Paras, A. Deole, A. S. Gandhi and K. M. Bhurchandi, “FM based indoor localization and mapping system with real-time implementation on FPGA,” 2015 International Conference on Information and Communication Technology Convergence (ICTC), 2015, pp. 176-181, doi: 10.1109/ICTC.2015.7354522. View Paper: IEEE

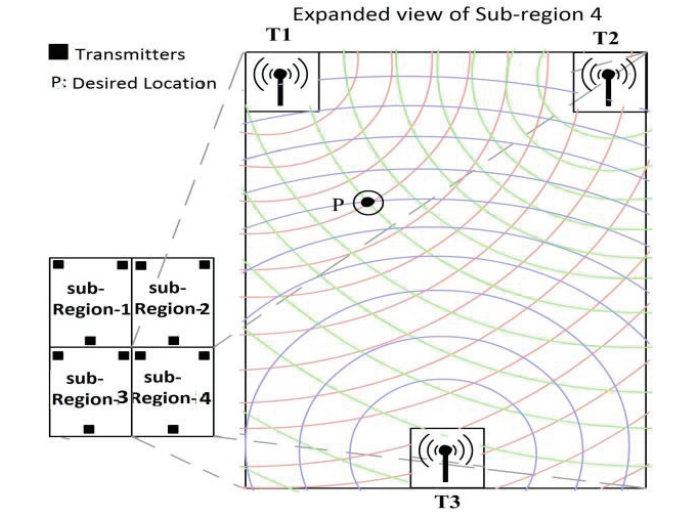

Description: Indoor localization and mapping has become very crucial part of pervasive computing in recent times. Conventional outdoor techniques using GPS, Wi-Fi, and Cellular Networks have proved expensive and unconventional for indoor mapping. This document presents unique method of real time indoor localization and mapping using FM and ASK wave transceivers implemented using Phased Locked Loop and Field Programmable Gate Array (FPGA). Localization is procured with respect to three FM transmitters tuned at different frequencies. The geometrical wave model of these transmitters renders family of circles, where radius of each circle represents ‘Received Signal Strength Indicator’ (RSSI) value corresponding to a particular transmitter. Solving this family of circles for a common point yields the location of object with respect to the transmitters. Object is installed with customized FPGA core and 3 FM receivers tuned to respective transmitter frequencies. RSSI values from each FM receiver are resolved into 4 bit digital values inclusively. FPGA acquire and process values from FM receivers via 3 parallel I2C buses which provide real time response. Unwanted continuous FM radiation is prevented by the use of wireless control over FM transmitters. Overall, a low cost solution is obtained to create a digital map which localizes and tracks objects in real-time.

A. Kulkarni and K. Bhurchandi, “Low Cost E-Book Reading Device for Blind People,” 2015 International Conference on Computing Communication Control and Automation, 2015, pp. 516-520, doi: 10.1109/ICCUBEA.2015.106. View Paper: IEEE

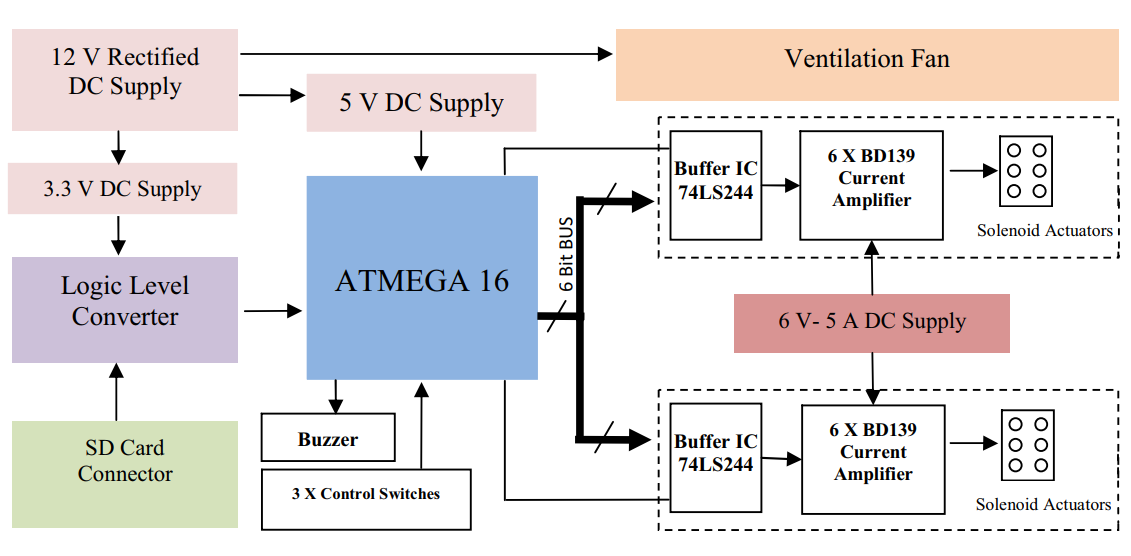

Description: The work outlines a device for visually impaired individuals to read e-books, featuring two electronic Braille display units. These units use a novel method involving six solenoid pin actuators to convert alphanumeric characters into Braille. Text is stored on a Secure Digital (SD) Card and displayed at a rate of 2 characters per second, allowing users to read by placing their hands on both units simultaneously.